特斯拉首席執(zhí)行官埃隆·馬斯克近日透露,公司自研AI芯片的迭代計(jì)劃已進(jìn)入關(guān)鍵階段。在宣布AI5芯片完成流片后,他詳細(xì)闡述了后續(xù)產(chǎn)品的技術(shù)路線圖,其中AI6與AI6.5芯片的制造工藝與架構(gòu)設(shè)計(jì)成為焦點(diǎn)。

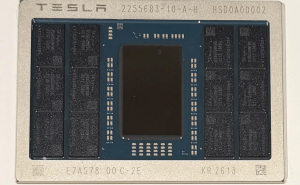

據(jù)馬斯克介紹,AI5芯片在算力上實(shí)現(xiàn)重大突破,單顆芯片的有效算力達(dá)到雙芯AI4方案的5倍。該芯片的內(nèi)存配置引發(fā)行業(yè)關(guān)注——兩側(cè)封裝的內(nèi)存顆粒長(zhǎng)寬比例異常,與GDDR系列標(biāo)準(zhǔn)不符,推測(cè)采用LPDDR5X規(guī)格。這一設(shè)計(jì)選擇或與芯片對(duì)低功耗、高帶寬的需求密切相關(guān)。

下一代AI6芯片將由三星電子位于美國(guó)得州泰勒市的晶圓廠代工,采用2nm制程工藝制造。在保持400平方毫米以上芯片面積的前提下,其性能較前代實(shí)現(xiàn)翻倍增長(zhǎng),并配備更新的LPDDR6內(nèi)存。更值得關(guān)注的是,AI6.5芯片將轉(zhuǎn)由臺(tái)積電美國(guó)亞利桑那州工廠生產(chǎn),同樣基于2nm工藝,通過(guò)架構(gòu)優(yōu)化進(jìn)一步推高性能極限。

在芯片架構(gòu)層面,AI6與AI6.5均采用創(chuàng)新設(shè)計(jì):約50%的TRIP AI計(jì)算加速器將與SRAM緩存實(shí)現(xiàn)緊密耦合。這種布局可顯著減少數(shù)據(jù)傳輸延遲,提升內(nèi)存訪問(wèn)效率,從而在相同功耗下獲得更高的實(shí)際運(yùn)算性能。行業(yè)分析師指出,這種異構(gòu)集成方式正成為高性能AI芯片的設(shè)計(jì)趨勢(shì)。